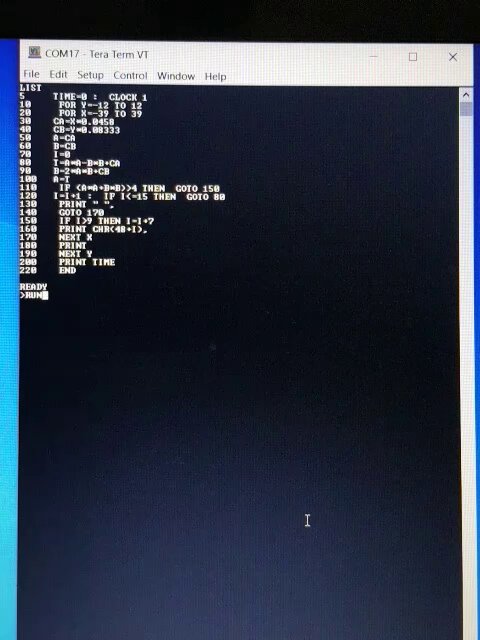

8052 VHDL softcore implementation on CYCLONE IV fpga. 12kB program memory and 4kB XRAM implemented on the FPGA running at 50MHz. BASIC-52 V1.31 + I2C and SFR implemented. ASCIIART takes 10.56 seconds. Maximum memory of 12kB ROM and 16kB RAM possible with this FPGA. #ASCIIART